**PRELIMINARY**

April 1982

## LM1981 AM Stereo Decoder

### **General Description**

The LM1981 is a single IC designed to decode the stereo information which is amplitude and angle modulated on an AM stereo broadcast carrier. It is capable of accepting the 455 kHz (or 262 kHz) IF amplifier output and amplitude detecting the (L+R) mono signal; limiting, detecting and conditioning the (L - R) stereo difference signal; and combining these signals in a suitable matrix to form the left and right channel audio outputs. Other features include an excess phase detector, stereo pilot tone output. stereo/mono blend function, output sample and hold circuits and an internally regulated reference voltage.

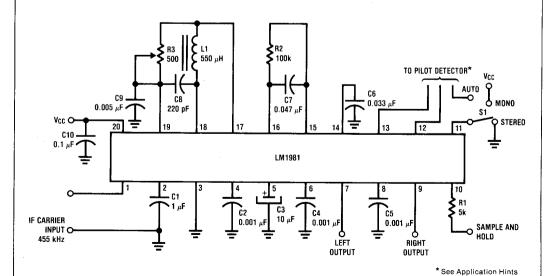

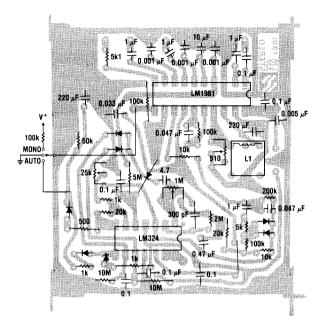

The 1 M1981 is shown in the circuit diagram of Figure 1. which includes typical external component values used with the signal format of the Magnayox AM/PM system.

Both left and right channel outputs (pins 9 and 7, respectively) are buffered with sample and hold circuits which can be used to hold the signal level in the presence of a detected noise burst.

The LM1981 AM stereo decoder is available in a 20-pin. molded dual-in-line package.

### **Features**

- Single chip AM stereo decoder

- Minimum external components

- Wide input dynamic range

- Full wave AM detector

- Quadrature PM detection

- Excess phase output

- Noise suppression circuitry

- Stereo pilot tone output

- Stereo/mono auto blend circuit

- Regulated reference output

- Available in plastic 20-pin DIP

## **Typical Application**

FIGURE 1. Magnavox System Decoder

### **Absolute Maximum Ratings**

Supply Voltage 18V Reference Output Current  $\pm 1 \, \text{mA}$ Minimum Voltage on Any Pin  $-0.1 \, V_{DC}$ Package Dissipation (Note 1) 1.67W Operating Temperature Range (Note 3) 0°C to 70°C 150°C Maximum Junction Temperature Storage Temperature Range -65°C to +150°C Lead Temperature (Soldering, 10 seconds) 230°C

#### **Electrical Characteristics**

V<sub>CC</sub> = 8V, T<sub>A</sub> = 25 °C, V<sub>IN</sub> = 200 mVrms, 30% AM, PM modulation depth, IF carrier frequency = 455 kHz, MOD = 1 kHz, pin 11 = GND

| Parameter                                            | Conditions                                        | Min      | Тур        | Max | Units                    |

|------------------------------------------------------|---------------------------------------------------|----------|------------|-----|--------------------------|

| Operating Supply Voltage Range                       | (Note 2)                                          | 8        |            | 18  | V <sub>DC</sub>          |

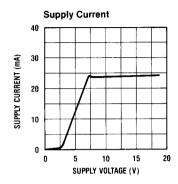

| Supply Current                                       | Figure 1, V <sub>CC</sub> = 8V, 18V               |          | 22         | 40  | mA                       |

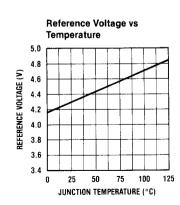

| Reference Voltage                                    | Pin 19                                            | 3        | 4.3        | 5   | V <sub>DC</sub>          |

| Input Impedance                                      | Pin 1                                             | 4        | 15         | 30  | kΩ                       |

| Input Signal Level<br>Minimum<br>Maximum             |                                                   |          | 20<br>400  |     | mVrms<br>mVrms           |

| Monaural Output                                      | Pin 11 = $V_{CC}$ , $V_{CC}$ = 8V, 18V            |          | 120        |     | mVrms                    |

| Monaural Distortion                                  | Pin 11 = $V_{CC}$ , 1 kHz,<br>$V_{CC} = 8V$ , 18V |          | 0.2        |     | %                        |

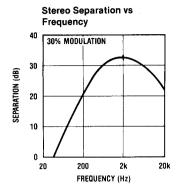

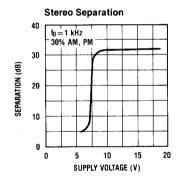

| Stereo Separation<br>Left<br>Right                   | 1 kHz, V <sub>CC</sub> = 8V, 18V                  | 20<br>20 | 30<br>30   | į   | dB<br>dB                 |

| Stereo Distortion                                    | V <sub>CC</sub> = 8V, 18V                         |          | 0.4        |     | %                        |

| Signal to Noise Ratio                                | CCIR                                              |          | 50         |     | dB                       |

| Output Current<br>Left<br>Right                      |                                                   |          | ±1<br>±1   |     | mA<br>mA                 |

| Pilot Tone Output                                    | Pin 13 (Note 3)                                   |          | 28         |     | μАр-р                    |

| Excess Phase Threshold                               |                                                   |          | 75         |     | Degrees                  |

| Excess Phase Output                                  | Pin 12, Input Phase = ± 100°                      |          | 100        |     | μΑ                       |

| Pin 12 Leakage                                       |                                                   |          | 0.1        |     | μΑ                       |

| Pin 4 Internal Resistance                            |                                                   |          | 2          |     | kΩ                       |

| Pin 5 Internal Resistance                            |                                                   |          | 9          |     | kΩ                       |

| Sample and Hold<br>Threshold Current<br>Slew Current | Pin 10<br>Pins 6, 8                               |          | 120<br>140 | 300 | μ <b>Α</b><br>μ <b>Α</b> |

| Limiter Output Current                               | Pin 17                                            |          | ± 130      |     | μΑ                       |

| Integrator Output Current                            | Pin 14                                            |          | ±1         |     | μΑ                       |

Note 1: For operation in ambient temperatures above 25°C, the device must be derated based on a 150°C maximum junction temperature and a thermal resistance of 75°C/W junction to ambient.

Note 2: Operating supply voltage range on specified tests only. Operation below  $0^{\circ}$ C may require  $V_{CC}$  to be >8V.

Note 3: Magnavox system employing a pilot modulation level of four radians at 5 Hz.

### External Components (Refer to Figure 1 Application Circuit)

| Component | ent External Component Function                                                                                                                                                                                                                                                                          |                  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| C1        | Input decoupling capacitor. Enables input amplifier and limiter to track dynamic offset voltages caused by large amplitude modulation of the carrier.                                                                                                                                                    | 0.47 μF-2.2 μF   |

| C2        | AM carrier filter. Sets the upper 3 dB corner of the bandwidth of the AM information. Internal resistance is approximately 2 k $\Omega$ . Increasing value will lower the bandwidth.                                                                                                                     | 0.001 μF-0.01 μF |

| C3        | IF carrier filter. DC voltage on this capacitor is proportional to average value of the IF carrier. Used to compensate AGC tracking irregularities.                                                                                                                                                      | 4.7 μF-47 μF     |

| C4, C5    | Sample and hold capacitors. Pin 6 and 8 output currents and capacitor values determine output slew rate capabilities. Not required if noise suppression circuitry is not utilized.                                                                                                                       | 0 pF-2000 pF     |

| C6        | Integrator capacitor to simulate large inductor across pins 15 and 16. Sets PM information bandwidth, low pass pole to identify pilot tone in stereo mode. Inversely proportional to C7.                                                                                                                 | 0.01 μF-0.047 μF |

| C7        | Integrating capacitor determining the (L $-$ R) detected level. This value and R3 determine degree of separation that is obtainable.                                                                                                                                                                     | 0.033 μF-0.1 μF  |

| C8        | Capacitor that, with L1, forms a series resonant circuit at the IF frequency. Value is determined by the drive current available at pin 17.                                                                                                                                                              | 100 pF-390 pF    |

| C9        | Supply decoupling capacitor.                                                                                                                                                                                                                                                                             | 0.05 μF-10 μF    |

| L1        | Quadrature coil. Value must resonate with C8 at the IF frequency.                                                                                                                                                                                                                                        | 200 μH-2000 μH   |

| R1        | Sample and hold resistor. Limits the current flow into pin 10, which is a diode to ground. If noise suppression is not used, R1 can be eliminated and pin 10 tied to ground.                                                                                                                             | 0-∞              |

| R2        | Prevents peaking in the low pass filter across pins 15 and 16.                                                                                                                                                                                                                                           | 51 kΩ-1 MΩ       |

| R3        | Determines detector conversion gain by dominating tuned circuit (L1, C8) Q if inductor series resistance is low. Normally approximately $200\Omega$ , it is shown as a potentiometer, to adjust for part-to-part variation in the multiplier operating currents, to avoid different levels of (L $-$ R). | 500Ω pot         |

| S1        | SP3T switch to select stereo, monaural, or automatic function. In the automatic mode, circuitry (see Application Hints) can use the blend characteristics of this input to adjust the degree of stereo demodulation depending upon the integrity of the received signal.                                 |                  |

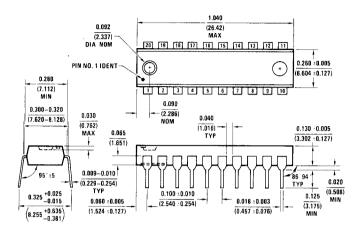

# **Connection Diagram**

#### **Dual-In-Line Package**

## **Typical Performance Characteristics**

## **Application Hints**

#### LM1981 CIRCUIT DESCRIPTION

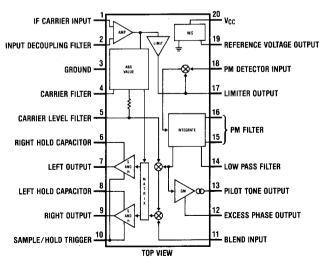

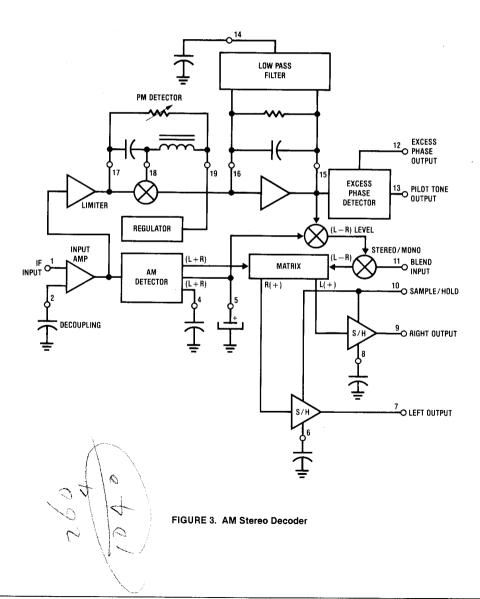

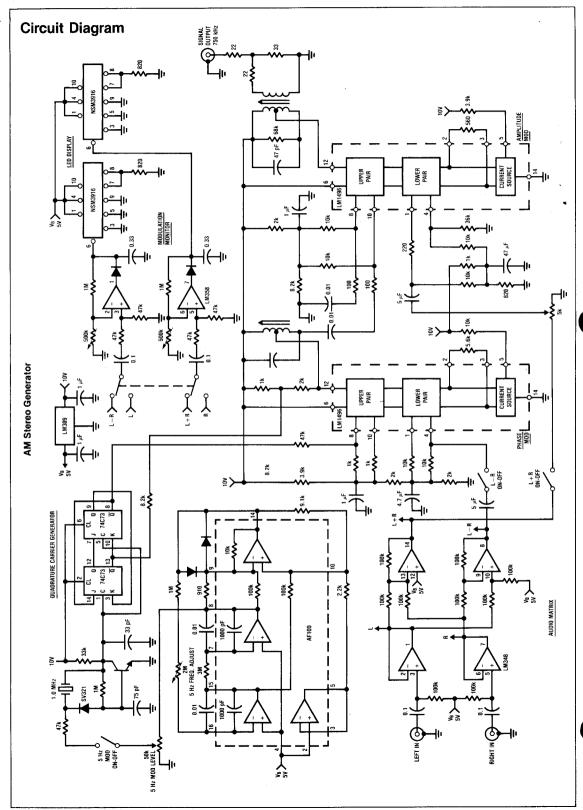

The basic features of the LM1981 are shown in the block diagram of *Figure 3*, which includes typical external component values used when the signal format is the Magnavox AM/PM system.

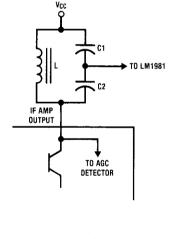

Usually the signal input to the LM1981 will be extracted from the final AM/IF amplifier tuned circuit. In this particular design example, the tank circuit impedance is required to be 15 k $\Omega$  and the 455 kHz carrier level is approx-

imately 400 mVrms when the RF signal strength is above the AGC threshold. From the table of Electrical Characteristics we see that the LM1981 input resistance is 15 k $\Omega$  and the nominal input level is 200 mVrms. The input stage is capable of handling signal levels +6 dB greater or -20 dB less than 200 mVrms which will ensure proper stereo operation until the signal S/N ratio is too low to be satisfactory.

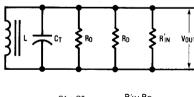

It is necessary for the IF amplifier final stage bandwidth to be relatively wide so that the IF bandwidth, which may be selectable, is determined by the previous stages. A suitable circuit with a take-off point for the LM1981 is shown in Figure 4, along with the equivalent circuit. If the IF amplifier output resistance (R<sub>O</sub>) is 100 k $\Omega$ , the tank will be damped by this and the parallel input resistance (R'<sub>IN</sub>) presented by the input resistance of the LM1981 reflected across the tank. Since the tap ratio will be 2:1 to provide the proper signal level to the LM1981, the reflected resistance R'<sub>IN</sub> is given by

$$\begin{array}{l} R'_{IN}=n^2R_{IN} \quad \therefore \ R'_{IN}=60 \ k\Omega \\ \text{and} \ R_t=R'_{IN}|| \quad R_D=37.5 \ k\Omega \end{array} \tag{10}$$

If we set the tuned circuit bandwidth at 20 kHz, the unloaded circuit Q is

$$Q_{L} = \frac{f_{o}}{\Delta f} = \frac{455 \times 10^{3}}{20 \times 10^{3}} = 23$$

Now the dynamic resistance ( $R_D$ ) of the tuned circuit in parallel with  $R_t$  must present a 15 k $\Omega$  load to the IF amplifier output

i.e.,

$$R_D || R_t = 15 \text{ k}\Omega$$

,  $\therefore R_D = 25 \text{ k}\Omega$

Since  $R_D$  also determines the unloaded Q of the tuned circuit

$$\frac{Q_L}{Q_u} = \frac{R_t}{R_t + R_D} \therefore Q_u = 38.3 \tag{11}$$

For a parallel resonant circuit we have

$$L = \frac{R_0}{\omega Q_u} \tag{12}$$

$$L = \frac{37.5 \times 10^3}{2\pi 455 \times 10^3 \times 38.3} = 228 \ \mu H$$

The total capacitance necessary to tune this inductance to 455 kHz is 536 pF, so each capacitor is put at 1000 pF.

Following the input stage, the signal is split up into two paths; one to a limiter for the angle modulated information and the other to an envelope detector for the amplitude modulated information. This latter detector is a full wave rectifier. Filtering the carrier component at pin 4 leaves the amplitude modulating information. Internally the resistance at pin 4 is 2 k $\Omega$  so that a 3900 pF capacitor sets the -3 dB bandwidth at 20 kHz. The output level for 30% modulation (200 mVrms IF) is 120 mVrms.

$$1/CT = \frac{C1 + C2}{C1 C2}$$

$Rt = \frac{R'_{IN} R_{O}}{R'_{IN} + R_{O}}$

FIGURE 4. LM1981 Input Circuit and Model

Although the (L+R) monophonic signal is available at pin 4, normally the signal for the audio amplifiers will be taken from the matrix which follows the detector. The detected output is heavily filtered at pin 5 to provide a DC voltage proportional to the average value of the IF carrier. Because the absolute value detector will not peak detect on noise, this voltage is an accurate indication of the IF carrier level and is used to compensate the detected level of the phase modulated (L – R) signal, which is insensitive to changes in the average carrier level caused by the AGC not perfectly tracking the RF signal strength. The internal load resistance at pin 5 is 9 k $\Omega$  so that a 10  $\mu$ F capacitor gives a 90 ms time constant.

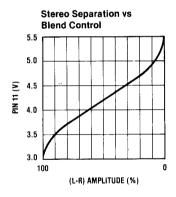

At the matrix the (L-R) signal is added to the (L+R) signal. The actual amplitude of the (L-R) signal will not only depend on the control voltage developed at pin 5, but also on the voltage at the blend input, pin 11. If pin 11 is held above the internal reference voltage (4.26V on pin 19) the (L-R) signal is completely muted and the left and right channel outputs will be (L+R) information only.

Both left and right channel outputs (pins 9 and 7, respectively) are buffered with sample and hold circuits, which can be used to hold the signal level in the presence of a detected noise burst. If pin 10 is left floating or grounded, the S/H circuits will pass the signal. Pulling pin 10 to a  $V_{\rm BE}$  above ground holds the pin 7 and pin 9 output levels. The capacitors for the S/H circuits are at pins 6 and 8, and these capacitors will slew limit the audio signal. The charge/discharge current is 140  $\mu{\rm A}$  so that for a 1V swing at 20 kHz

$$C_{PIN 6.8} \le 0.0022 \,\mu F$$

In the PM channel, the signal passes through 5 stages of limiting before being applied to the detector circuit. The limiter is stabilized with DC feedback decoupled at pin 2. Although the carrier switching frequency is relatively low, the capacitor at pin 2 is relatively small to enable it to track dynamic offset voltages in the limiter caused by the simultaneous large amplitude modulation of the carrier.

The signal is FM detected in a quadrature demodulator and then integrated by C7 in Figure 1. The limited amplitude RF carrier signal switches one set of balanced input ports to the multiplier, while the other ports are receiving the signal after it passes through a resonant circuit tuned to the carrier frequency. A series resonant circuit is used, driven from a current source in order to minimize radiation at the carrier frequency. Since this available signal current is typically 130  $\mu$ A (peak), the capacitor, C8, is chosen to ensure switching amplitude (about 400 mVp-p at the multiplier inputs).

$$|\omega C| \ge \frac{260 \times 10^{-6}}{400 \times 10^{3}} \ge 0.65 \times 10^{-3}$$

∴C≤227 pF

Choosing C to be 220 pF gives the inductor nominal value as

$$L = \frac{1}{(2\pi \times 455 \times 10^3)^2 220 \times 10^{-12}} = 556 \ \mu H$$

Although both sets of input ports to the multiplier are switched, the conversion gain can change since the multiplier operating currents are internally set. In order to avoid different levels of (L - R) from part to part we need to

provide some external means of adjusting the detector conversion gain. This is most conveniently done by a potentiometer connected across the tuned circuit which will dominate the circuit Q if the inductor series resistance (R<sub>O</sub>) is low. With a coil  $Q_u$  of 110,  $R_D=14.5\Omega$  at 455 kHz. If we choose a tuned circuit bandwidth of  $\pm$  30 kHz then the loaded Q will be 7.5. For a series tuned circuit with a shunt resistance R we have

$$\frac{Q_L}{Q_U} = \frac{R_D}{R + R_D} \tag{13}$$

and the potentiometer resistance will be approximately 193 $\Omega$ . Now that suitable components have been chosen for the resonant circuit that yield a gain adjustment and the proper bandwidth, it becomes possible to select the integrating capacitor which gives the nominal (L – R) detected level necessary for best separation. With a 500 $\Omega$  pot set to 200 $\Omega$  the capacitor value is 0.047  $\mu$ F.

Also connected across the multiplier output is an active inductor which serves a two-fold purpose. First, it places a DC short across the multiplier outputs, preventing offset voltages exceeding the dynamic range of the next stage. These offsets can occur because of mismatching in the multiplier active devices but, more importantly, as the tank circuit is tuned for resonance (or the input signal is mistuned) DC terms are present in the multiplier output which must be cancelled if the output linear operating range is not to be exceeded. Secondly, the inductor is tuned with the integrating capacitor to produce a low frequency pole in the output. Since we would like some means for detecting excess phase signals for noise suppression purposes, the detected stereo identification tone peak voltage must be reduced below the peak audio voltage (remember, in the Magnavox system, the detected audio is riding up and down on a 5 Hz waveform that is 4 times the peak audio amplitude). This is done by choosing the pole frequency to be around 30 Hz. The capacitor has already been determined as 0.047 µF, so a 30 Hz pole requires that the inductor be almost 600H! Hence an active inductor is used.

Two operational transconductance amplifiers (OTAs) are used to realize the simulated inductor. The actual inductance value is proportional to the size of the capacitor at pin 14 such that

$$L = C \cdot k$$

(14)

$k = 1.8 \times 10^{10} H/\mu F$

For 600H, we need a 0.033  $\mu$ F capacitor. A 100 k $\Omega$  resistor is shunted across pins 15 and 16 to prevent peaking in the low pass filter.

Alignment of the detector (in fact the entire alignment for the decoder) is straightforward. The blend input is shorted to ground and the coil is tuned for resonance at 455 kHz by adjustment until the voltage on the capacitor at pin 14 matches the reference voltage at pin 19. Because the charge current for the capacitor is only 1  $\mu$ A, this point is easily loaded and the best way to connect a DVM is between pins 14 and 19 rather than from pin 14 to ground. Next, with left only or right only information modulating the carrier, the potentiometer between pins 17 and 19 is adjusted for maximum separation. For example, with right only signals, the potentiometer is set to minimize the left output signal at pin 9. At 1 kHz, 30% PM, the left signal level should be - 30 dB down.

The detected (L - R) signal is connected internally to the matrix through a variable gain block controlled by the average level of the IF carrier—the voltage developed at pin 5. By this means, the separation adjustment carried out above will not be impaired by the AGC characteristics of the receiver. A second gain control is placed between the (L - R) signal and the matrix. This gain block is controlled by the mute/blend input at pin 11 and enables stereo/mono switching or a gradual blend from stereo to mono as the RF signal deteriorates. The control amplifier is equivalent to a differential pair biased at  $V_{\rm REF}$  with 5 k $\Omega$  between the bases and a series 50 k $\Omega$  to pin 11. For a 100 mV differential across the pair

$$V_{PIN 11} \ge V_{REF} \pm 100 \times 10^3 \times \left(\frac{50+5}{5}\right) = V_{REF} \pm 1.1V_{REF} = 1.1V_$$

A control curve is shown in the typical performance graphs and, above 5.36V, the decoder will be in the mono mode; below 3.16V the decoder will be in the stereo mode.

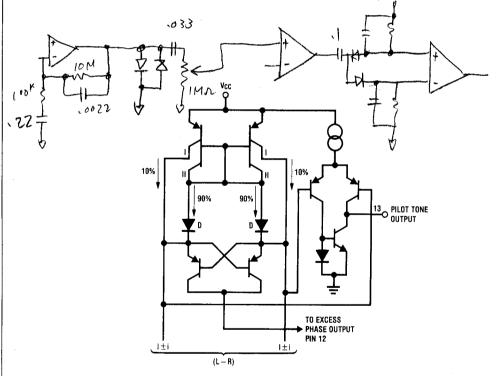

The last part of the decoder to be described is the PM output and excess phase detector, Figure 5. A buffered differential (L-R) signal current from the PM integrating capacitor is supplied to this circuit which has a DC to AC

ratio such that each degree of detected phase deviation causes a 1.2% change in the current drawn from each side of the detector. For each side, with no signal, 10% of the total current is supplied by collector I of the upper PNP device. The remaining 90% is supplied by collector II through a diode D. When a signal is present, as the peak phase deviation increases, one side will draw more current and the other side correspondingly less. The differential current component is buffered to pin 13 to provide an output for the stereo identification tone detector. A 30% modulated audio signal will cause pin 13 to sink and source 54  $\mu A$  and the stereo identification tone, reduced in level by the PM detector low pass filter, produces 14  $\mu A$  peak.

When the peak phase deviation exceeds 75° this indicates that noise must be present and the peak current drawn in one side is less than 10% of the quiescent value. Collector II will be transferring all of its current to the other side (which will be drawing greater than 190% of the quiescent current) and the diode for collector II will cut off. The difference between the current demanded, and that delivered by collector I is coupled over to pin 12 which then provides an excess phase indication.

FIGURE 5. Excess Phase Detector

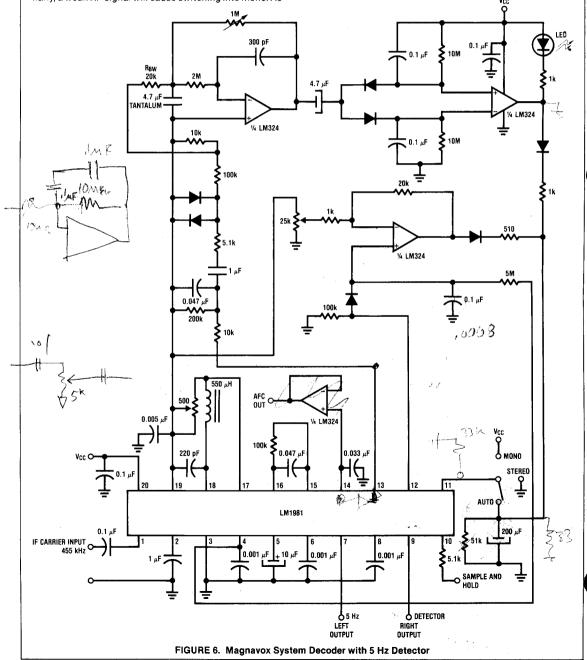

A complete Magnavox system decoder is shown in Figure 6, including a suggested stereo tone detector. This consists of a 5 Hz filter followed by a full wave rectifier connected to the stereo/mono blend input pin 11. The excess phase output is filtered and applied to pin 11, as is a filtered voltage from the absolute value detector. Excess phase outputs will force pin 11 above V<sub>REF</sub>, giving automatic switching into mono in the presence of noise in the PM channel. Similarly, a weak RF signal will cause switching into mono. As

Blan

the RF signal improves, the DC level at pin 4 will go below  $V_{\rm REF}$  enabling the stereo mode if a stereo tone is simultaneously present.

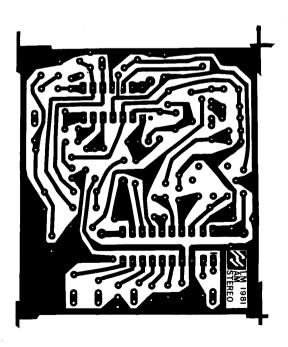

A complete decoder PCB for the Magnavox system, based on the circuit of *Figure 6* is shown in *Figure 7* along with a component stuffing guide. Set-up is straightforward, following the procedure outlined earlier.

Component Side

Copper Side -

FIGURE 7. Magnavox Decoder PCB

### Physical Dimensions inches (millimeters)

Molded Dual-In-Line Package (N) Order Number LM1981N NS Package Number N20A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive

2900 Semiconductor Drive Santa Clara, California 95051 Tel: (408) 737-5000\* TWX. (910) 339-9240 \*After June 6, 1982 Cali (408) 721-5000

National Semiconductor GmbH Furstenriederstrasse Nr.5 8 Munchen 21 West Germany Tel: (089) 56 01 20

Telex. 522772

NS Japan K.K. POB 4152 Shinjuku Center Building 1-25-1 Nishishinjuku, Shinjuku-ku Tokyo 160, Japan Tel.: (03)349-0811 National Semiconductor (Hong Kong) Ltd. 1st Floor, Cheung Kong Electronic Bldg 4 Hing Yip Street Kwan Tong Kowloon, Hong Kong Tel.: 3-899235 Telex: 43866 NSEHK HX

Cable: NATSEMI HX

Notasi Lida. Avda Brigadeiro Faria Lima 830 8 ANDAR 01452 Sao Paulo, Brasil Tel.: 212-1181 Telex: 1131931 NSBR

National Semiconductores

NS Electronics Pty. Ltd. Cnr. Stud Rd. & Mtn. Highway Bayswater, Victoria 3153 Australia Tel.: 03-729-6333 Telex: 32096